Lattice Diamond 軟件開發(fā)流程(上)

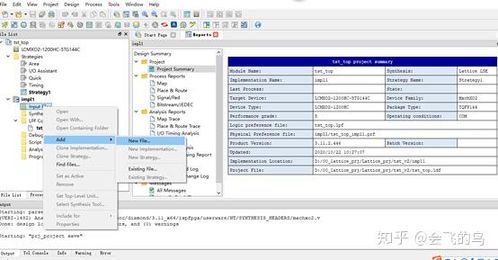

Lattice Diamond 軟件是萊迪思半導體(Lattice Semiconductor)公司推出的一款集成開發(fā)環(huán)境(IDE),廣泛用于其FPGA和CPLD器件的設(shè)計、仿真和編程。本部分為軟件開發(fā)流程的上篇,主要介紹從項目創(chuàng)建到邏輯設(shè)計的關(guān)鍵步驟。

- 項目創(chuàng)建與配置

- 啟動 Lattice Diamond 軟件后,首先需創(chuàng)建一個新項目。在項目向?qū)е校脩粜枰付椖棵Q、存儲路徑,并選擇目標器件型號(如 iCE40、ECP5 等系列)。

- 配置項目設(shè)置,包括設(shè)計語言(如 Verilog、VHDL 或原理圖輸入)、綜合工具選項和約束文件管理。正確配置是后續(xù)設(shè)計成功的基礎(chǔ)。

- 設(shè)計輸入

- 用戶可通過多種方式輸入設(shè)計:使用硬件描述語言(HDL)編寫代碼,或利用圖形化原理圖編輯器。對于復雜設(shè)計,推薦采用模塊化 HDL 編碼,以提高可讀性和可維護性。

- 在輸入過程中,需確保代碼符合語法規(guī)范,并遵循萊迪思器件的特定設(shè)計指南,避免不支持的語法或結(jié)構(gòu)。

- 綜合與優(yōu)化

- 設(shè)計輸入完成后,進入綜合階段。Diamond 軟件內(nèi)置綜合工具(如 Synplify Pro 或 Lattice LSE)將 HDL 代碼轉(zhuǎn)換為門級網(wǎng)表。

- 在綜合設(shè)置中,用戶可啟用優(yōu)化選項,如面積優(yōu)化、時序優(yōu)化或功耗優(yōu)化,以匹配項目需求。綜合報告應仔細檢查,識別潛在問題如未連接端口或時序違規(guī)。

- 設(shè)計仿真

- 在實現(xiàn)硬件之前,必須進行功能仿真以驗證邏輯正確性。Diamond 支持集成仿真工具(如 ModelSim),用戶可編寫測試平臺(Testbench)模擬輸入信號并觀察輸出。

- 仿真結(jié)果應覆蓋關(guān)鍵場景,確保設(shè)計在預期條件下正常工作。如果發(fā)現(xiàn)錯誤,需返回設(shè)計輸入階段進行修改。

- 約束管理

- 約束文件(如物理約束和時序約束)是指導布局布線的關(guān)鍵。用戶需定義引腳分配、時鐘頻率和時序路徑要求。

- 在 Diamond 中,可通過圖形界面或手動編輯約束文件(如 .lpf 文件)來應用約束,確保設(shè)計滿足實際硬件接口和性能指標。

以上步驟涵蓋了 Lattice Diamond 軟件開發(fā)流程的前半部分,從項目初始化到設(shè)計驗證。在下一篇中,我們將繼續(xù)討論布局布線、比特流生成和器件編程等后續(xù)流程。通過遵循這些步驟,開發(fā)者可以高效地完成 FPGA/CPLD 設(shè)計,縮短產(chǎn)品上市時間。

如若轉(zhuǎn)載,請注明出處:http://www.landmy.com.cn/product/1.html

更新時間:2026-03-09 22:58:20